當正常的程序執行流程發生暫時的停止時,稱之為異常,處理器允許多個異常同時發生,它們将會按固定的優先級進行處理。

ARM 體系結構所支持的異常類型ARM 體系結構中的異常,與8 位/16 位體系結構的中斷有很大的相似之處,但異常與中斷的概念并不完全等同。

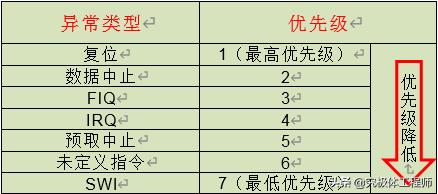

當多個異常同時發生時,ARM9 處理器将按照異常的優先級高低順序處理,異常優先級由 高到低 的排列次序如表所示。

異常發生會使得正常的程序流程被暫時停止,例如ARM9 處理器響應IRQ 異常 。

處理器進入異常處理程序前,應該保存其當前的狀态,以便當異常處理程序完成後,處理器能回到原來程序的斷點處繼續執行。

對異常的響應

1、将下一條指令的地址存入相應鍊接寄存器LR ,以便程序在處理異常返回時能從正确的位置重新開始執行。

(1)若異常是從ARM 狀态進入,LR 寄存器中保存的是下一條指令的地址(當前PC +4 或PC +8 ,與異常的類型有關);

(2)若異常是從Thumb 狀态進入,則在LR 寄存器中保存當前PC 的偏移量,這樣,異常處理程序就不需要确定異常是從何種狀态進入的。

2、将CPSR 複制到相應的SPSR中。

3、根據異常類型,強制設置CPSR 的運行模式位。

4、強制PC 從相關的異常向量地址取下一條指令執行,從而跳轉到相應的異常處理程序處,同時設置中斷禁止位,以禁止中斷發生。

注意:

如果異常發生時,處理器處于Thumb 狀态,則當異常向量地址加載入PC 時,處理器自動切換到ARM

異常返回

異常處理完畢之後,ARM 微處理器會執行以下幾步操作從異常返回:

⑴将鍊接寄存器LR 的值減去相應的偏移量後送到PC 中。

⑵将SPSR 複制回CPSR 中。

⑶若在進入異常處理時設置了中斷禁止位,要在此清除。

注意:

恢複CPSR 的動作會将T 、F 和I 位自動恢複為異常發生前的值。

下表總結了進入異常處理時保存在相應R14(LR )中的PC 值,及在退出異常處理時推薦使用的指令。

異常的響應及返回

應用程序中的異常處理當系統運行時,異常可能會随時發生,為保證在ARM 處理器發生異常時不至于處于未知狀态,在應用程序的設計中, 首先 要進行異常處理,采用的方式是在異常向量表中的特定位置放置一條跳轉指令,跳轉到異常處理程序, 當ARM 處理器發生異常時 ,程序計數器PC 會被強制設置為對應的異常向量,從而跳轉到異常處理程序, 當異常處理完成以後 ,返回到主程序繼續執行。

下面以圖示的方式演示進入和退出異常的過程

進入和退出異常的過程進入異常

1、程序在系統模式下運行用戶程序,假定當前處理器狀态為 Thumb 狀态、允許 IRQ 中斷

置位I 位(禁止 IRQ 中斷)

清零T 位(進入 ARM 狀态)

設置 MOD 位,切換處理器模式至 IRQ模式

将下一條指令的地址存入IRQ 模式的 LR 寄存器

将跳轉地址存入 PC ,實現跳轉

2、用戶程序運行時發生 IRQ 中斷,硬件完成以下動作:

将CPSR寄存器内容存入IRQ模式的SPSR寄存器

置位I 位(禁止 IRQ 中斷)

清零T 位(進入 ARM 狀态)

設置 MOD 位,切換處理器模式至 IRQ 模式

将下一條指令的地址存入IRQ 模式的 LR 寄存器

将跳轉地址存入 PC ,實現跳轉

進入異常

退出異常

在異常處理結束後,異常處理程序完成以下動作:

将 SPSR 寄存器的值複制回CPSR 寄存器

将 LR 寄存的值減去一個常量後複制到 PC 寄存器,跳轉到被中斷的用戶程序。

退出異常

,更多精彩资讯请关注tft每日頭條,我们将持续为您更新最新资讯!